Program/Erase Cycling Enhanced Lateral Charge Diffusion in Triple-Level Cell Charge-Trapping 3D NAND Flash Memory | Semantic Scholar

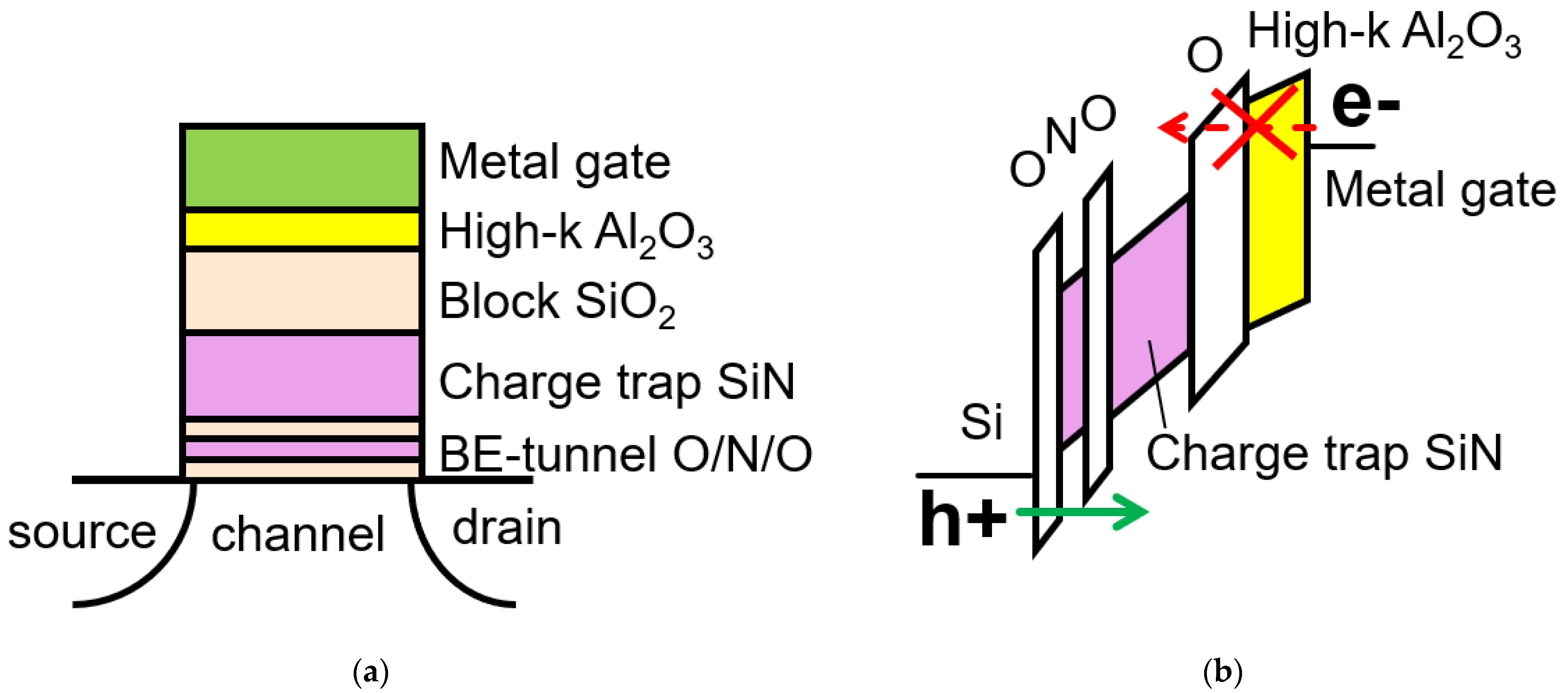

Nanomaterials | Free Full-Text | Optimal Energetic-Trap Distribution of Nano-Scaled Charge Trap Nitride for Wider Vth Window in 3D NAND Flash Using a Machine-Learning Method

Color online) Schematic energy band diagram of fully programed charge... | Download Scientific Diagram

Investigation of charge-trap memories with AlN based band engineered storage layers | Semantic Scholar

Figure 4 from Nonvolatile Poly-Si TFT Charge-Trap Flash Memory With Engineered Tunnel Barrier | Semantic Scholar

Charge‐Trap Flash‐Memory Oxide Transistors Enabled by Copper–Zirconia Composites - Baeg - 2014 - Advanced Materials - Wiley Online Library

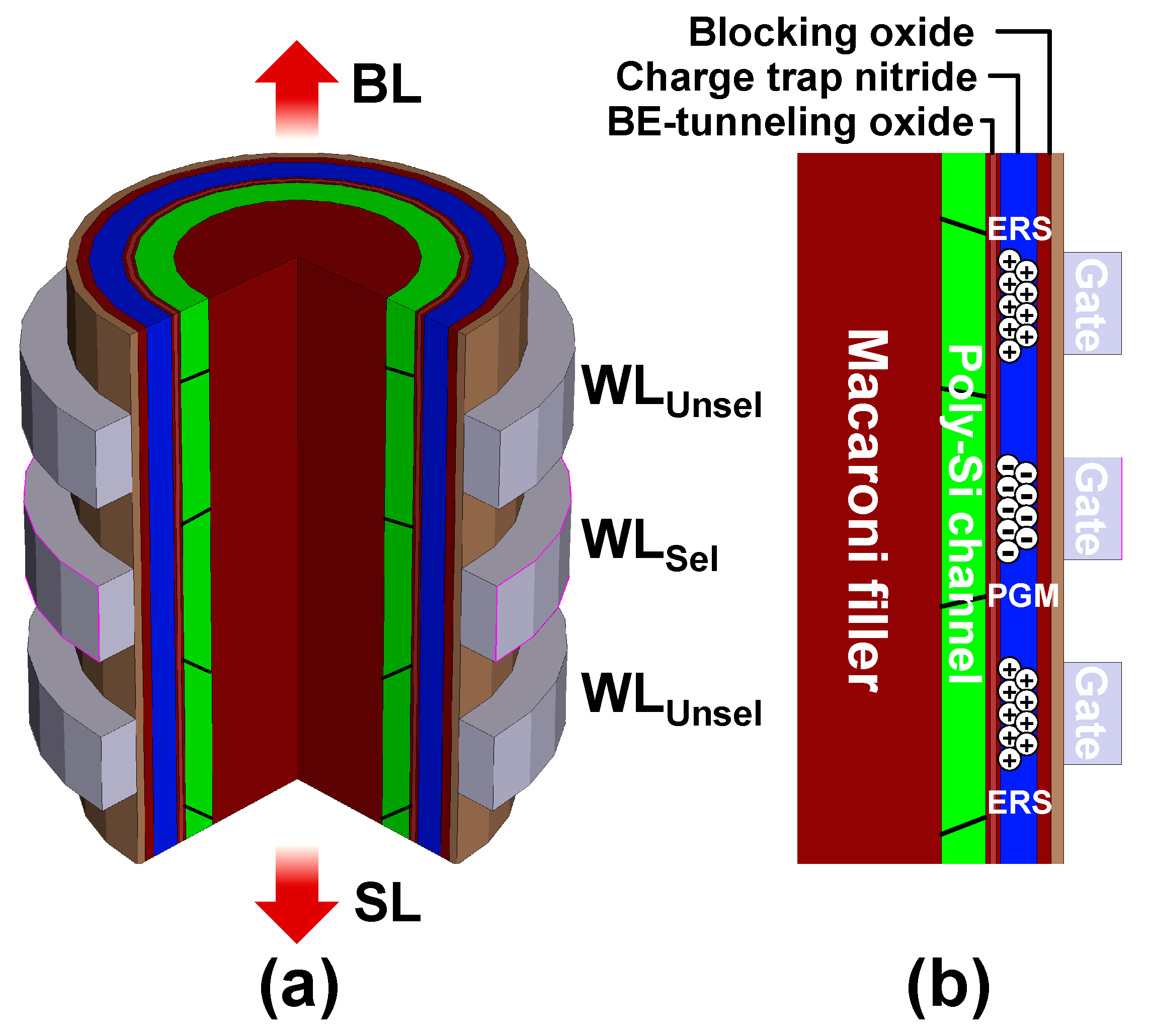

Characterization Summary of Performance, Reliability, and Threshold Voltage Distribution of 3D Charge-Trap NAND Flash Memory | ACM Transactions on Storage

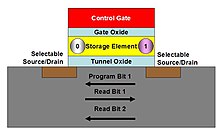

![2001.07424] Investigation of Data Deletion Vulnerabilities in NAND Flash Memory Based Storage 2001.07424] Investigation of Data Deletion Vulnerabilities in NAND Flash Memory Based Storage](https://ar5iv.labs.arxiv.org/html/2001.07424/assets/fg2.png)